In the era of rapid advancements in communication technology, terminal application scenarios are becoming increasingly diverse and undergoing continuous iteration and renewal.

Artificial intelligence (AI) technology continues to evolve, driving terminal products toward greater intelligence, lighter and thinner designs, and higher frequency and speed capabilities.

This trend is driving printed circuit boards (PCBs) toward higher density, precision, and performance.

PCB manufacturing technology must urgently evolve to accommodate greater layer counts, denser routing, narrower line widths, and increased high-speed signal lines.

High-density interconnect (HDI) technologies such as build-up (BU), blind/buried vias, any-layer HDI (ALHDI), and back drilling emerged in response to these demands.

By overcoming numerous critical technical challenges, these innovations collectively propel the advancement of the printed circuit board manufacturing industry, providing robust support for the realization of various high-end electronic devices.

Issues with Existing Technologies

Currently, the manufacturing process for HDI boards is lengthy, with problems present in each step, specifically as follows:

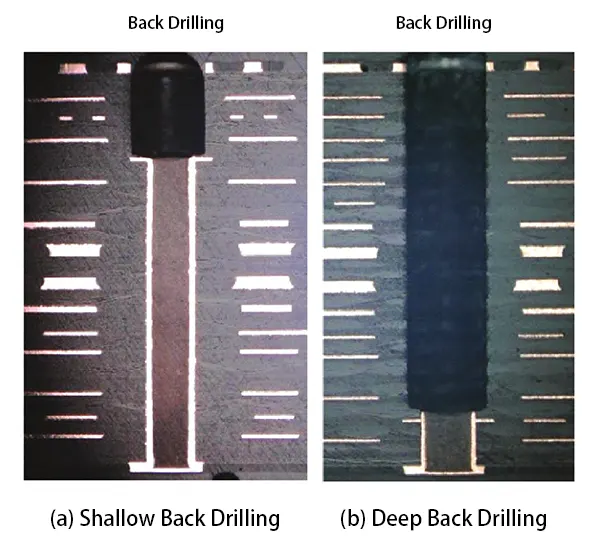

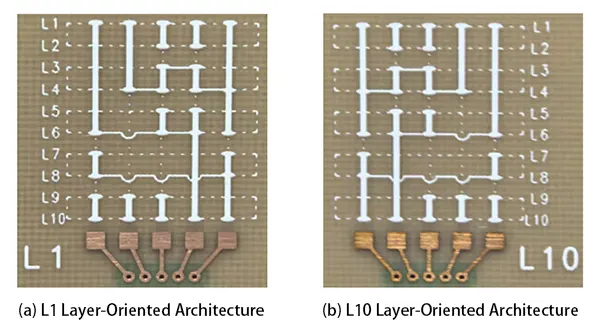

1. The layer-by-layer lamination process is an advanced stacking technology for producing high-density multilayer PCBs (HDI boards), enabling arbitrary interconnection of layers in both core-based and core-free boards, as shown in Figure 1.

It constructs circuit layers through “sequential stacking.”

After completing one layer, the steps of “lamination-drilling-electroless copper plating-pattern formation” are repeated to incrementally add circuit layers, ultimately forming the required multilayer structure.

This process requires multiple lamination and plating cycles.

Repeated positioning operations introduce cumulative positioning errors, resulting in complex procedures and high scrap rates due to accumulated defects.

2. Blind/buried via technology involves vias that do not penetrate the entire board thickness, reducing space requirements and increasing routing density.

These vias are formed through laser and mechanical drilling, requiring drilling after each lamination process.

Multiple drilling operations increase labor hours and product defect rates.

Laser drilling becomes more challenging with thicker copper layers, while mechanical drilling faces difficulties in depth control.

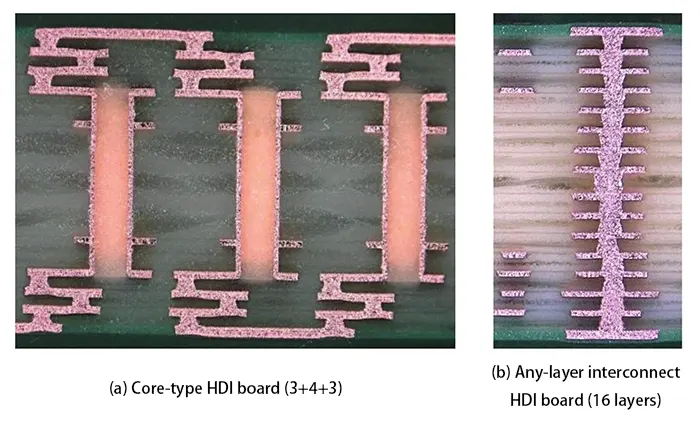

3. The back drilling process aims to optimize signal integrity by removing unnecessary plated-through hole wall plating—known as stubs—through controlled-depth drilling.

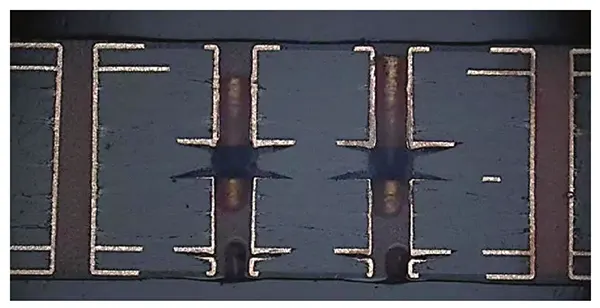

The cross-section of a back drilled hole is shown in Figure 2. Typically, mechanical drilling uses board thickness or the table surface as the reference for drilling depth.

However, localized variations in board thickness lead to poor depth control accuracy, making it difficult to achieve stub-free results.

Additionally, this method suffers from low processing efficiency and poor positioning accuracy during secondary drilling.

Conceptual Framework for Through-Hole Interconnect Structures on Any Layer

Employing the “First Principles” approach involves reasoning and problem-solving from fundamental principles, setting aside experience and analogy to return to the most basic principles or facts of a matter, then deriving conclusions based on these principles.

The fundamental principle of circuit boards is enabling signal routing.

Regardless of complexity—from single-sided boards to 20-layer HDI boards—their essence lies in connecting solder pads via traces to form current/signal networks.

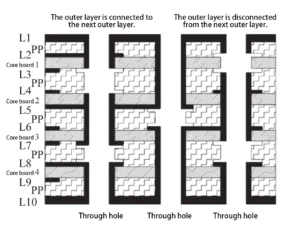

Solder pads exist only on the outer two layers, with traces bridging these layers through vias to inner layers.

Vias occupy significant space within a PCB. Achieving multiple signal transmissions through a single via reduces the number of layers and vias required.

This approach necessitates only one lamination, drilling, and plating process, substantially lowering manufacturing costs and process complexity. The structure described is illustrated in Figure 3.

Implementation of Through-Hole Interconnection Structures on Any Layer

PCB Structural Design

An indented isolation ring is placed at each end of the through-hole within the isolation strip requiring interlayer insulation.

This isolation ring consists of an isolation disc on the inner core layer with a height of 5–50 μm, where the ratio of etching depth to width exceeds 5.

When a via’s two isolation strips share a via wall copper layer connecting at least two inner layers, this copper segment links to the via wall copper layer of another via through inner layer traces, ultimately connecting to the outer layer traces.

Manufacturing Process

1. Inner Layer Fabrication and Laminating

Circuit boards composed of multiple laminated core layers are provided, with pre-designed drill hole positions.

Before lamination, an alkali-soluble ultraviolet (UV) curable ink is coated onto the inner surface of the core layer corresponding to the isolation ring, forming an isolation disc.

2. Drilling and Etching

Through-holes are drilled at designated positions on the circuit board to expose the inner layer isolation discs.

Subsequently, an etching process removes the isolation discs within the holes, forming isolation rings.

During etching, the circuit board is immersed in a 10% sodium hydroxide solution at 60°C for 30 to 120 minutes.

3. Copper Plating and Electroplating

To ensure complete isolation of the isolation zone, the steps are as follows:

(1) Perform chemical copper plating followed by DC flash plating.

The layer formed by chemical copper plating at the isolation ring exhibits poor conductivity.

DC flash plating parameters are: current density 0.8–1.5 ASD, duration 3–6 min, to thicken the copper layer on the hole walls by 1–3 μm.

(2) Remove the copper layer from the isolation zone using either the first pulse electroplating or micro-etching treatment.

The total pulse electroplating duration is 6 min, with a forward pulse current density of 3 ASD (10 ms) and a reverse pulse current density of 9 ASD (10 ms).

The reverse pulse can be integrated with DC flash plating and plating thickening; the reverse pulse is preferred. Micro-etching involves immersing the circuit board in a micro-etching solution, controlling the etch depth to 0.8–1.6 μm.

Micro-etching is suitable for factories without pulse plating production equipment.

Due to the thin copper layer at the isolation ring, the reverse pulse dissolution rate exceeds the forward deposition rate.

Once the copper layer on the insulating substrate is removed, it cannot be redeposited, thereby achieving copper connection severance.

(3) Finally, perform DC plating or a second pulse plating. Pulse plating thickens the layer to the design thickness;

DC plating increases the via copper thickness by 30 μm, thereby forming an interconnect structure between any layers of the through-hole.

First Trial Production

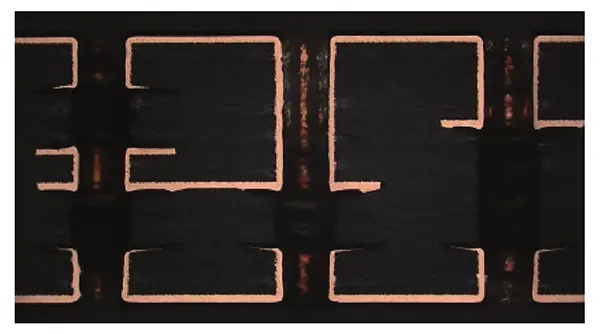

During the first trial production, an inner connecting disc was installed on the isolation strip.

Due to incomplete separation between the connecting disc and the etched recess, copper plating occurred on the isolation strip (see Figure 4).

Second Trial Production

During the second trial production, the etched areas exhibited extensions of both the chemical copper and electroplated copper layers, with the extended ends forming pointed tips (see Figure 5).

Third Prototype

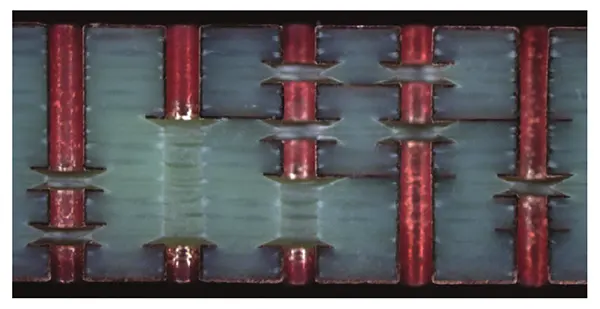

The third prototype achieved multiple networks within a single hole.

The sample and structure are shown in Figure 6, with cross-sections depicted in Figure 7.

Reliability Verification

To ensure the effectiveness and reliability of the technology in practical applications, a series of verification activities must be conducted.

Specifically, After sample manufacturing is completed, physical testing is performed, including electrical performance testing (e.g., impedance testing, signal transmission speed testing), mechanical performance testing (e.g., vibration resistance testing, temperature endurance testing), and environmental adaptability testing.

Through verification, process parameters and design solutions are optimized to ensure the circuit board meets actual application requirements.

Manufacture multilayer boards with interlayer isolation following the above process flow, and test the reliability of inner layer connections.

Test method: Oil immersion test—immerse in 260°C silicone oil for 10 seconds, then transfer to 20°C silicone oil for 20 seconds, repeating this cycle 200 times.

Test results: Inner-layer conductive via plating demonstrated excellent continuity, maintaining reliable connections after 200 oil immersion cycles.

Additionally, a series of reliability tests—particularly conductive anodic filament (CAF) testing—must be conducted to ensure long-term product reliability and stability.

Development Path of Through-Hole Interconnection Technology for Any Layer

Through-hole interconnection for any layer requires only one lamination, drilling, and plating process to achieve interconnection between any layers.

It is gradually replacing drilling, mechanical drilling of blind/buried vias, and laminated processes, offering the following advantages:

(1) No design data modification required; directly replaces drilling to achieve no residual posts.

(2) When replacing blind/buried vias, client-side data modification is required to reroute traces crossing different networks around the through-hole (by adding isolation rings within the hole).

(3) When replacing step-up lamination, besides modifying traces on other layers, micro-drilling is required.

Micro-drill bits reach a minimum diameter of 50 μm, or UV laser drilling can be employed to create the through-hole.

Challenges Encountered in Through-Hole Interconnection Technology Across Any Layer

During the implementation of this process, the following issues frequently arise:

(1) End customers must incorporate new structural concepts during the product design phase.

They should recognize that this novel design reduces PCB layer count and via quantity, significantly lowering manufacturing costs and shortening lead times while improving yield rates and product reliability.

Specific optimizations to the client’s product structure involve: in the original design, routing traces on other layers around or over the through-hole (by placing isolation discs within the through-hole).

(2) CAM script optimization. Currently, isolation disc positions are manually added, resulting in large data volumes and high error rates.

Therefore, the product’s computer-aided manufacturing (CAM) system script must be upgraded to enable automated parameter settings for isolation discs, thereby improving design efficiency.

(3) Inkjet ink material optimization. Although existing text inkjet inks are UV-curable, their alkali solubility is poor, requiring extended soaking times.

Therefore, technical collaboration with ink suppliers is necessary to optimize alkali solubility, reduce heat-curing properties, and customize alkali-soluble UV-curable inks tailored to this process, ensuring effective isolation.

(4) PCB Manufacturing Process Optimization. Dedicated inkjet printing equipment must be integrated with production lines to enhance efficiency.

Optimize electroplating conditions, particularly reverse pulse plating parameters.

The above four technical improvements require collaborative advancement among end customers, PCB manufacturers, material suppliers, and CAM software developers to establish a closed-loop technical ecosystem spanning the entire supply chain.

This cross-industry deep collaboration not only accelerates technology implementation but also drives efficiency gains and cost optimization across the entire electronics manufacturing industry chain through standardized process specifications.

Conclusion

This paper proposes a through-hole interconnect circuit board with arbitrary layer connectivity and its manufacturing method: at least two isolation discs are placed at the drilling positions, followed by sequential processes including drilling, etching, copper plating, and electroplating.

This forms copper-free isolation strips between adjacent isolation rings, retaining only segmented, separated copper layers on the hole walls within the through-holes.

This structure enables multiple independent signal transmissions within the same through-hole, achieving reliable interconnectivity between arbitrary layers.

Compared to conventional processes, this method eliminates the need for multiple lamination, drilling, copper plating, and electroplating steps, significantly reducing manufacturing costs and simplifying the production workflow.