Image sensing technology is widely applied across diverse scenarios such as medical, industrial control, and automotive fields.

As image sensors evolve toward thinner, lighter, and smaller components, the design requirement for embedding sensing chips and active or passive electronic components into printed circuit boards (PCBs) has emerged.

To achieve embedded assembly of electronic components, corresponding PCBs require the design of cavities (CV).

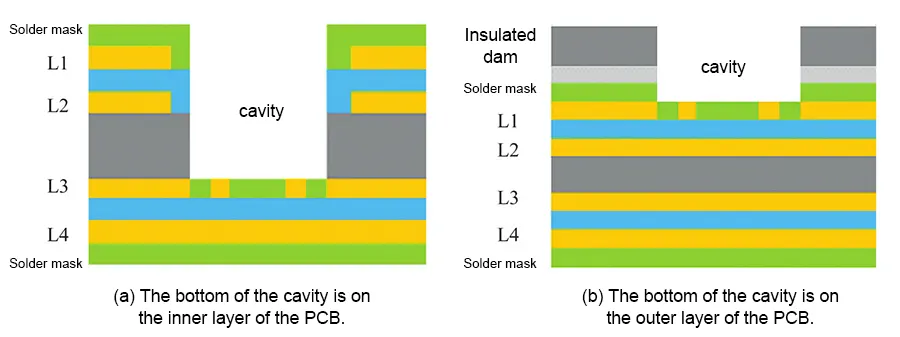

Depending on requirements, the cavity bottom pattern can be designed on either the inner or outer layers of the PCB, as shown in Figures 1 and 2.

Depending on the packaging method, the cavity bottom circuit pattern is designed as a solder pad for surface mount technology (SMT) applications, or as a bonding pad for chip-on-board (COB) packaging.

This study uses a camera module PCB as an example, where the cavity bottom pattern is designed on the PCB outer layer for COB packaging.

It details the manufacturing process flow and technical challenges encountered, providing reference for the industry.

Product Features and Processing Challenges

Product Features

The industry-standard COB packaging process involves: first applying a dam sealant along the chip mounting area edges on the PCB surface, then bonding the chip with metal wires, and finally completing the encapsulation.

This product eliminates the dam process by pre-forming recesses on the PCB surface (see Figure 2).

After bonding the chip to the PCB surface within the recess, the encapsulation resin is directly injected into the recess.

Challenge Analysis

Based on the product’s primary characteristics, its processing challenges and analysis are presented in Table 1.

| No. | Key Difficulty | Difficulty Analysis |

|---|---|---|

| 1 | Gold/Nickel Thickness Control | The surface finish is gold plating. The plated area ratio between the bottom side (B side) and the top side (T side) is approximately 20:1. The large difference in plating area between the two sides can easily lead to non-uniform plating thickness, resulting in the gold/nickel layer thickness exceeding specifications. |

| 2 | Warpage Control in Asymmetric Lamination | After slot milling of the optical substrate, it is laminated with a 4-layer PCB to form a cavity. The structures on both sides create an asymmetric stack-up, which can easily cause warpage (see Figure 2). |

| 3 | Pure Adhesive Lamination Parameters and Reliability Evaluation | The optical substrate is laminated with a 4-layer PCB using pure adhesive to form a cavity structure. It is necessary to evaluate the lamination parameters of the pure adhesive process and assess product reliability. |

Table 1 – Analysis of Major Manufacturing Difficulties of the Product

Gold Plating Process

This product features a gold-plated (pure gold) surface treatment, suitable for wire bonding and solder welding.

It simultaneously meets COB packaging requirements and surface mount technology (SMT) needs.

Gold-Plated Lead Design

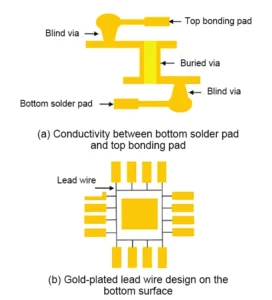

Network analysis reveals that all bonding pads on the top surface are interconnected with selected solder pads on the bottom surface through blind and buried vias, forming a unified network as shown in Figure 3(a).

To establish electrical connectivity between all bottom-side solder pads and top-side bonding pads, gold-plated leads must be arranged within the bottom-side unit, as illustrated in Figure 3(b).

Solder mask openings must be designed at lead locations to facilitate subsequent etching processes for lead removal.

Conventional Gold Plating Process and Existing Issues

The conventional gold plating process is designed as follows:

Outer layer circuit etching → Solder mask process → Secondary pattern transfer (dry film covering leads) → Gold plating (including nickel/gold plating) → Film stripping → Alkaline etching of leads → Post-processing.

The manufacturing challenge lies in the following:

The bottom-side gold-plated pads with larger plating areas have sparse power lines, while the top-side gold-plated pads with smaller plating areas have densely packed power lines.

Consequently, when the gold-nickel thickness on the bottom side is too thin, the gold-nickel thickness on the top side tends to be excessively thick.

After conventional gold plating, a random panel was selected. Gold/nickel thickness was measured at five points per side using the five-point method.

The measurement data is shown in Table 2, where “T” represents the top side and “B” represents the bottom side.

As shown in Table 2, the measurement results do not meet the requirements.

| Requirement | Surface | Panel 1 | Panel 2 | Panel 3 | Panel 4 | Panel 5 | Max | Min | T/B Difference | Judgment |

|---|---|---|---|---|---|---|---|---|---|---|

| Gold Thickness 0.5–1.0 | Top (T) | 1.27 | 1.24 | 1.12 | 1.26 | 1.09 | 1.27 | 1.09 | 0.82 | Fail |

| Bottom (B) | 0.45 | 0.48 | 0.50 | 0.52 | 0.55 | 0.55 | 0.45 | |||

| Nickel Thickness 5.0–10.0 | Top (T) | 9.30 | 9.47 | 11.32 | 10.95 | 12.14 | 12.14 | 9.47 | 6.88 | Fail |

| Bottom (B) | 5.26 | 5.76 | 5.35 | 5.68 | 6.01 | 6.01 | 5.26 |

Table 2 – Gold/Nickel Thickness Measurement Data

Solution Design

Based on the above analysis, three improvement solutions are proposed. The specific solutions and evaluation results are shown in Table 3.

| Scheme | Scheme Design | Advantage/Disadvantage Analysis | Conclusion |

|---|---|---|---|

| 1 | Adjust the conventional panel layout to a yin–yang (alternating flip) panelization, meaning the T side and B side of adjacent boards are alternately flipped so that the plated areas on both sides of the working panel are approximately equal. | Advantage: Maintain the original single plating process while improving gold thickness uniformity; low processing cost. Disadvantage: In this structure, the T side forms a cavity when laminated with the optical substrate, making it difficult to unify the panel orientation during processing. | Not suitable for this product |

| 2 | Remove part of the copper foil area on the T side of the working panel to increase the plating area, thereby reducing the plating area difference between the T side and B side. | Advantage: Maintain the single plating process and improve gold thickness uniformity. Disadvantage: Increasing the gold-plated area in the removed copper region raises manufacturing cost. | Feasible, but higher cost |

| 3 | Change the process to two separate gold-plating steps: Process flow: Solder mask → adhesive tape masking (B side only) → first gold plating (T side only) → remove tape → second pattern transfer (dry film covering both T and B traces) → second gold plating (B side only) → strip film → alkaline etching of circuit → subsequent processes. | Advantage: Two-step plating allows control of plating area difference. Disadvantage: Adds an extra gold-plating step as well as tape masking and removal processes, increasing cost. | Feasible, cost lower than Scheme 2 |

Table 3 – Evaluation of Improvement Schemes for Gold/Nickel Thickness Uniformity

Improvement Effect

Following a comprehensive evaluation, this product was manufactured using the optimized improvement plan 3.

The measured thickness data for the gold/nickel layer is shown in Table 4.

The results indicate that both gold and nickel thicknesses meet customer requirements, with the thickness variation of the gold/nickel layer showing significant improvement compared to the conventional process.

| Requirement | Surface | Panel 1 | Panel 2 | Panel 3 | Panel 4 | Panel 5 | Maximum | Minimum | T/B Difference | Judgment |

|---|---|---|---|---|---|---|---|---|---|---|

| Gold Thickness 0.5–1.0 | T Side | 0.78 | 0.84 | 0.73 | 0.78 | 0.82 | 0.84 | 0.73 | 0.27 | Qualified |

| Gold Thickness 0.5–1.0 | B Side | 0.58 | 0.57 | 0.58 | 0.64 | 0.63 | 0.64 | 0.57 | 0.27 | Qualified |

| Nickel Thickness 5.0–10.0 | T Side | 8.15 | 7.62 | 8.22 | 7.86 | 7.64 | 8.22 | 7.82 | 2.18 | Qualified |

| Nickel Thickness 5.0–10.0 | B Side | 6.35 | 6.28 | 6.04 | 6.27 | 6.38 | 6.38 | 6.04 | 2.18 | Qualified |

Table 4. Measurement Data of Gold/Nickel Thickness for Improvement Plan 3

Control of Concave Cavity Manufacturing Process

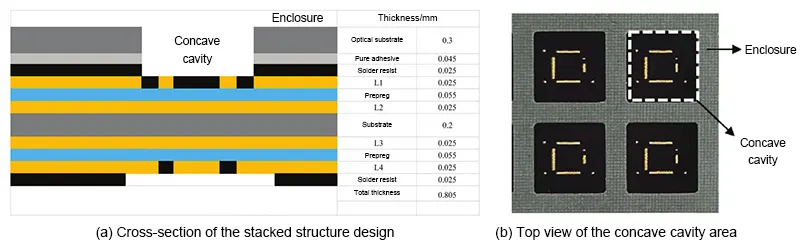

As shown in Figure 2(a), this product’s laminated structure consists of a 4-layer PCB, pure adhesive, and a milled-groove bare substrate (without copper foil laminate) after initial pressing.

When one side of the 4-layer PCB is bonded to the bare substrate and pressed, an asymmetrical structure forms, making warping prone to occur.

Warpage Control

1. Problem Description

After lamination with a light-transmitting substrate on one side, the 4-layer PCB forms an asymmetrical structure.

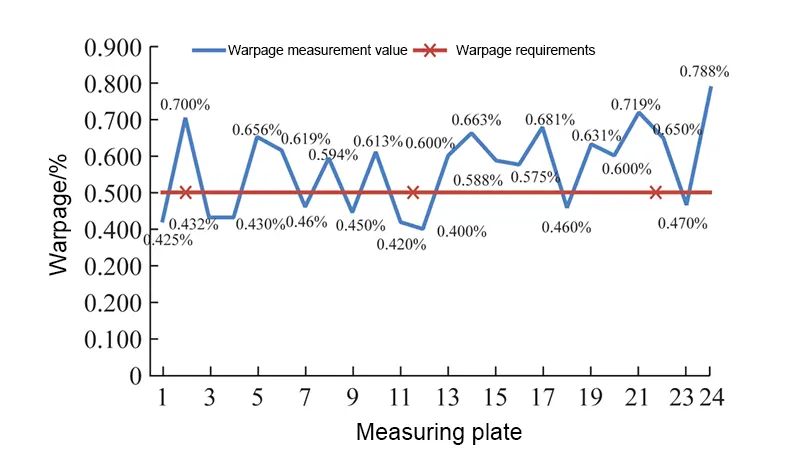

The warpage direction manifests as significant shrinkage on the light-transmitting substrate (T-side), creating a concave surface and posing a risk of warpage defects. The product’s warpage tolerance is ≤0.5%.

Four working boards were laminated using the conventional stacking method, as shown in Figure 4(a).

After forming, 24 delivery boards were milled. Full warpage inspection using a board warpage tester revealed 15 boards with warpage exceeding tolerances, resulting in a defect rate of 62.5%.

Specific warpage measurement results are shown in Figure 5.

2. Improvement Measures

For warpage mitigation, conventional methods involve extending cold pressing time; however, this approach yields limited effectiveness for significantly asymmetrical laminates.

This paper addresses the issue by optimizing the pressing and stacking methodology.

As shown in Figure 4(a), the conventional stacking method omits buffer materials.

In contrast, this approach incorporates silicone pads as buffer materials on the optical substrate side during intermediate layer lamination (Figure 4(b)).

The elasticity of the silicone pads induces a conforming effect during pressing, restraining the optical substrate’s contraction.

This reduces the substrate’s shrinkage rate, thereby mitigating warpage issues.

3. Improvement Results

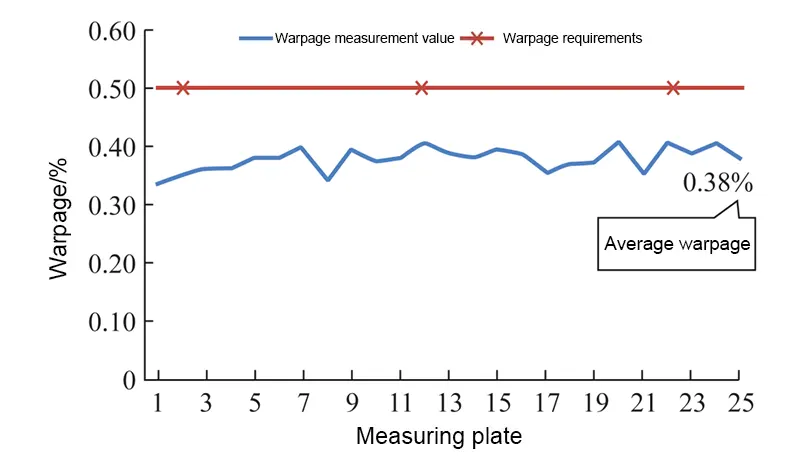

Twenty-four delivery boards were produced according to the optimized laminating plan, with no warpage exceeding tolerance limits.

The average warpage was controlled at 0.38%, as shown in Figure 6.

Pure Adhesive Laminating Parameters and Reliability Assessment

Pure adhesive exhibits excellent heat resistance, superior adhesion, low flowability, and minimal overflow.

Selecting pure adhesive as the secondary laminating medium facilitates alignment between optical substrates and PCBs while controlling overflow in recessed grooves.

Evaluating pure adhesive lamination parameters is critical for product reliability.

During lamination, parameter compliance was assessed based on material temperature profiles.

Post-lamination reliability validation was conducted, with results shown in Table 5.

| Item | Processing Guideline Reference Range | Test Result | Judgment |

|---|---|---|---|

| Press Temperature (°C) | 90–110 | 105 | Acceptable |

| Heating Rate (°C·min⁻¹) | 2–3 (90–160 °C) | 2.53 | Acceptable |

| Holding Time (≥160 °C) (min) | 90 | 115 |

Table 5 indicates that lamination parameters meet processing guideline requirements.

Post-lamination visual inspection and reliability test results are shown in Figure 7, demonstrating full compliance with requirements.

No surface defects such as pits, bubbles, or adhesive shortages were detected during visual inspection, and gold plating was satisfactory.

The measured adhesive overflow in the recess cavity was 74.26 μm, meeting the requirement of ≤150.00 μm.

After six reflow soldering reliability tests, no delamination defects were observed.

Conclusion

This paper analyzes the manufacturing challenges of a product featuring a patterned design on the bottom of a concave cavity with a gold-plated surface finish.

It proposes improvement solutions and verifies each step.

By implementing a two-sided, separate gold plating approach, the issue of uneven gold/nickel layer thickness on both sides was effectively resolved.

The warping caused by asymmetric lamination was resolved by stacking boards with buffer material added to one side.

By evaluating the lamination parameters for pure adhesive, the reliability of the cavity-containing product formed through secondary lamination met customer requirements.

In summary, these improvement measures proved effective, resolving the manufacturing challenges associated with cavity-containing PCB designs while ensuring their reliability.