In the design and manufacturing of printed circuit boards (PCBs), delay lines serve as critical components in communication and radar systems, playing a vital role in regulating signal delays.

Delay lines primarily consist of transmission lines and associated circuitry, precisely controlling signal propagation time through the physical length and material properties of the transmission lines.

In communication systems, delay lines compensate for signal transmission time differences to enhance signal synchronization and transmission quality.

Their high precision and low loss characteristics ensure stable, distortion-free signals during delay, thereby laying a solid foundation for the efficient operation of modern communication and detection technologies.

Such products primarily achieve signal delay by incorporating microstrip lines of varying lengths within PCB inner layers.

Their core performance metrics are phase and loss.

As frequency increases, controlling phase consistency becomes progressively challenging, making accurate prediction of phase shifts neither simple nor routine.

Furthermore, multiple factors during PCB design and manufacturing influence phase behavior.

Through experimental design, this paper systematically investigates the impact of four critical factors—board expansion/contraction, delay line copper thickness, number of delay line corners, and delay line edge roughness—on PCB delay line phase.

The objective is to determine the influence level of each factor on PCB delay line phase, thereby exploring effective methods for controlling phase consistency and providing reference for delay line circuit design and production.

Experimental Design Plan

Design Plan for Phase Effects of Expansion/Contraction and Copper Thickness

Design striplines of varying lengths on the same board (straight lines, excluding corner effects).

Using the shortest length as the baseline, calculate the relationship between phase and line length by measuring the phase difference between two striplines and their actual lengths.

In production, actual trace lengths can be calculated based on expansion/contraction, then converted into phase shift values.

By progressively reducing copper thickness, L4 layers with varying copper thicknesses (preset at three levels: 18 μm/25 μm/31 μm) are obtained.

Delay line traces are fabricated on these layers, and test boards are prepared to verify the phase shift effects of different copper thicknesses.

During etching, variations in etch rates and side etching severity across different copper thicknesses made it challenging to maintain consistent edge roughness and contour accuracy.

For instance, design corners could develop burrs that affected phase.

To minimize unnecessary errors, both this experiment and the expansion/contraction study employed patterns consisting solely of straight lines.

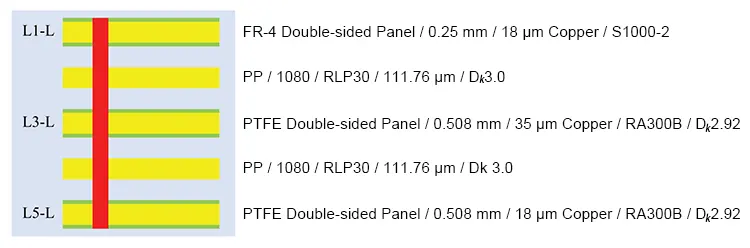

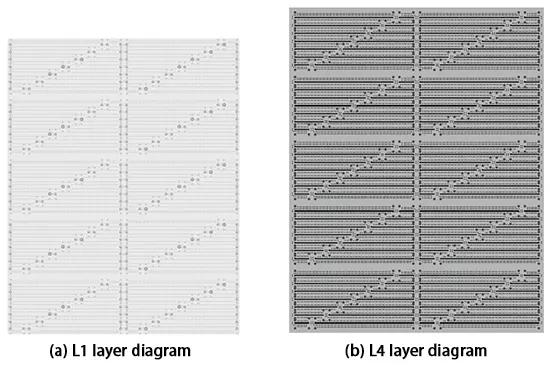

The laminate and pattern designs for the experimental boards verifying expansion/contraction and copper thickness effects are shown in Figures 1 and 2, respectively.

In the circuit design, apart from the patterns on layers L1 and L4 shown in Figure 2, layers L3 and L5 are blank layers.

Layers L2 and L6 serve as large copper ground planes, while layer L4 is the stripline layer (featuring striplines with lengths of 10, 20, 30, 40, 50, 60, and 70 mm).

Additionally, following the customer’s design specifications, shielding vias with a 0.3 mm hole edge clearance are placed on both sides of the striplines.

Experimental Design for Phase Effects of Delay Line Corner Count and Line Corner Burrs

Configure varying corner counts on a single board to validate phase impact from 0 to 10 corners.

Each corner count features 10 samples. Derive the phase-to-corner count relationship formula through fitting.

By altering the etching speed of the delay line’s L4 layer, printed circuit boards with varying corner burrs were produced to validate their phase impact.

Burr length was measured using a line width tester, with the longest dimension recorded.

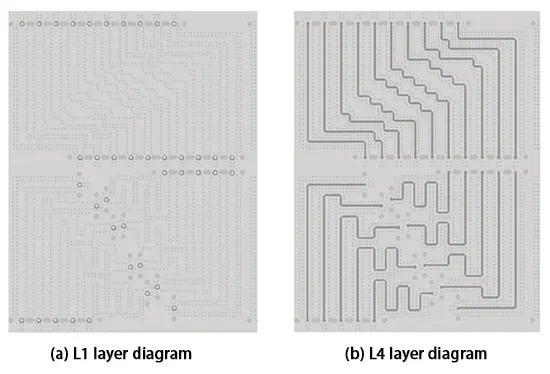

The laminate and pattern designs for boards verifying the phase effects of corner counts and burr sizes are shown in Figures 1 and 3.

Except for the patterns on layers L1 and L4 shown in Figure 3, layers L3 and L5 are blank layers, layers L2 and L6 are large copper ground planes, and layer L4 is a stripline layer (designed with striplines having corner counts of 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, 10, with corners designed as right angles with 45° external chamfers per customer specifications).

Additionally, shielding vias with 0.3 mm edge spacing were placed on both sides of the striplines per customer design.

Data Collection and Analysis

Data Collection and Analysis of Phase Effects from Expansion/Contraction and Copper Thickness in Delay Lines

1. Delay Line Copper Thickness Data

Following the experimental plan, different delay line copper thicknesses were achieved on the L3-L4 core boards by reducing copper.

The results for the L4 layer delay line copper thickness on three boards are shown in Table 1.

As indicated in Table 1, the three copper thickness levels corresponded to the expected values of 18 μm, 25 μm, and 31 μm.

| No. | Measurement 1 (μm) | Measurement 2 (μm) | Measurement 3 (μm) | Measurement 4 (μm) | Measurement 5 (μm) | Average (μm) |

|---|---|---|---|---|---|---|

| Board 1 | 31.2 | 31.6 | 31.5 | 31.4 | 31.6 | 31.46 |

| Board 2 | 25.6 | 25.0 | 25.7 | 25.4 | 25.3 | 25.4 |

| Board 3 | 19.1 | 18.9 | 18.6 | 18.2 | 18.4 | 18.64 |

Table 1. Copper Thickness Data of L4 Delay Line Traces

2. Phase Data Collection and Analysis

The finished board in this experimental setup employs a vector network analyzer, a Molex 732520090 adapter, and 9.5 GHz frequency testing to collect phase data for each stripline.

Since phase test data cannot monitor phase differences exceeding 360°, Based on signal transmission principles, longer lines incur greater propagation delays, resulting in an inverse relationship between absolute phase and line length.

Thus, each additional wavelength increases the phase measurement by 360° relative to the actual value.

Following this principle, phase data for three copper thicknesses were finalized, with results shown in Table 2.

| No. / Board | 10 mm | 20 mm | 30 mm | 40 mm | 50 mm | 60 mm | 70 mm |

|---|---|---|---|---|---|---|---|

| Board 1 (°) | -168 | -366 | -566 | -765 | -965 | -1163 | -1362 |

| Board 2 (°) | -168 | -367 | -567 | -765 | -965 | -1164 | -1363 |

| Board 3 (°) | -168 | -366 | -566 | -765 | -964 | -1164 | -1362 |

Table 2. Phase Summary for Three Copper Thicknesses at Designed Trace Lengths

Calculation of Actual Trace Length Considering PCB Expansion

Based on the actual expansion/contraction data of the test board at 6.7/10,000, the actual board trace length is the design value plus the elongation caused by expansion/contraction.

Taking 10 mm as an example, the final trace length is 10 × (1 + 0.00067) = 10.0067 mm.

Similarly, the actual finished lengths for each designed delay line are obtained. Specific data is shown in Table 3.

| Designed Trace Length (mm) | 10 | 20 | 30 | 40 | 50 | 60 | 70 |

|---|---|---|---|---|---|---|---|

| Actual Trace Length (mm) | 10.0067 | 20.0134 | 30.0201 | 40.0268 | 50.0335 | 60.0402 | 70.0469 |

Table 3 Actual Line Length Data for the Board

Phase–Length Fitting Analysis

In summary, the analysis concludes as follows:

(1) Substituting the line length and phase data into the fitting equation yields y = −20x + 31.

The slope of the line is −20°, meaning that for every 1 mm difference in line length, the absolute phase decreases by 20°.

The phase change equals the length change multiplied by (−20).

Therefore, in actual production, PCB expansion/contraction directly affects the delay line length, ultimately causing phase deviation in the printed circuit board.

Controlling PCB expansion/contraction consistency can effectively ensure phase consistency in the delay line printed circuit board.

(2) Phase data across all three copper thicknesses showed no significant differences, with deviations within 1°, indicating that delay line copper thickness has no effect on phase.

In actual PCB production, delay line copper thickness requires no special control.

Corner Count of Delay Lines and Phase Impact of Line Corner Burrs: Data Collection and Analysis

1. Analysis of Phase Impact from Delay Line Corner Count

The finished boards in this experimental setup employed a vector network analyzer and Molex 732520090 adapters to measure phase data for each stripline at 9.5 GHz.

Measurements revealed that the number of corners affects phase by no more than one wavelength.

If the effect exceeds one wavelength, the raw measurement values require normalization correction by subtracting one wavelength (360°) to ensure data accuracy and comparability.

After data processing, the phase results are presented in Table 4.

In summary, the analysis is summarized as follows: Linear fitting of the data shown in Table 4 yields the equation y = 7.3x – 185, indicating that each additional bend increases the phase by 7.3°.

Based on the expansion/contraction formula derived earlier: Phase change = Length change × (-20), this translates to a line length of 0.365 mm.

Thus, each additional bend shortens the line length by 0.365 mm.

Since the number of bends is determined by design, the impact of bend count on the final phase must be considered during the design phase.

| Number of Chamfer Angles | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|

| Phase (°) | -178 | -173 | -162 | -157 | -147 | -143 | -132 | -128 | -118 | -113 | -182 |

Table 4 — Phase Data for Different Number of Chamfer Angles

2. Data Collection and Analysis of Phase Effects from Delay Line Corner Burr Size

Table 5 summarizes the measured burr dimensions and corresponding phase data from four etched L3-L4 delay line boards.

Note that 1 mil = 25.4 μm, with all measurements converted accordingly.

| No. | Test Item | Board 1 | Board 2 | Board 3 | Board 4 |

|---|---|---|---|---|---|

| 1 | Burr Size (mil) | 1.17 | 2.45 | 2.94 | — |

| Phase (°) | -176 | -174 | -172 | -175 | |

| 2 | Burr Size (mil) | 1.52 | 1.74 | 1.71 | 2.78 |

| Phase (°) | -178 | -175 | -179 | -179 | |

| 3 | Burr Size (mil) | 1.22 | 1.42 | 1.69 | 2.45 |

| Phase (°) | -176 | -175 | -176 | -174 | |

| 4 | Burr Size (mil) | 1.35 | 1.26 | 1.66 | 1.84 |

| Phase (°) | -176 | -174 | -179 | -177 | |

| 5 | Burr Size (mil) | 1.19 | 1.08 | 1.39 | 1.44 |

| Phase (°) | -173 | -177 | -176 | -172 | |

| 6 | Burr Size (mil) | 2.56 | 1.38 | 1.31 | 1.86 |

| Phase (°) | -172 | -177 | -175 | -171 | |

| 7 | Burr Size (mil) | 1.39 | 3.16 | 1.71 | 2.35 |

| Phase (°) | -175 | -171 | -171 | -174 | |

| 8 | Burr Size (mil) | 1.17 | 1.63 | 1.42 | 2.08 |

| Phase (°) | -175 | -174 | -176 | -178 | |

| 9 | Burr Size (mil) | 1.30 | 1.69 | 1.16 | 2.15 |

| Phase (°) | -173 | -176 | -175 | -172 | |

| 10 | Burr Size (mil) | 1.57 | 1.66 | 1.33 | 1.73 |

| Phase (°) | -175 | -175 | -176 | -177 |

Table 5 : Phase Data for Different Burr Sizes

In summary, the analysis is summarized as follows:

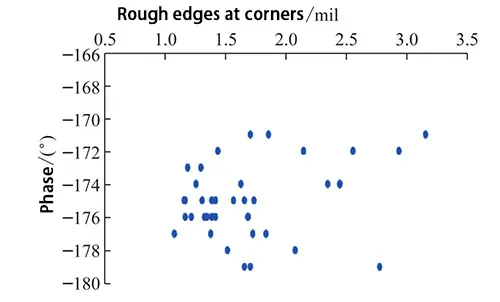

(1) Minitab Correlation Analysis of PCB Delay Line Phase and Burr Size

Using Minitab to perform correlation testing on the data in Table 5, the correlation coefficient was 0.230 (<0.300) with a P-value of 0.044 (<0.050).

This indicates that the phase of the PCB delay line is unrelated to the size of burrs.

The data distribution is shown in Figure 4.

(2) Burr Size Grouping Analysis Confirms No Impact on PCB Delay Line Phase

Group the data from Table 5 with burr sizes in the dense distribution range of 1.0–1.5 mil and 1.5–2.0 mil.

The average burr size for the 1.0–1.5 mil group is 1.29 mil, with an average phase of −175.1°, while the 1.5–2.0 mil group had an average burr size of 1.72 mil and an average phase of −175.4°.

The difference of only 0.3° falls below the phase accuracy requirement of 1°, further validating that phase is independent of burr size.

Conclusion

To address phase consistency issues in delay line circuit boards, this paper thoroughly investigates the specific effects of four factors on delay line phase: board expansion/contraction, delay line copper thickness, number of delay line corners, and delay line edge roughness.

The following conclusions are drawn:

(1) PCB delay line phase exhibits a strong correlation with actual trace length and the number of delay line corners.

Therefore, during design and manufacturing of delay line PCBs, minimize the number of corners and optimize trace layout to reduce phase delay.

In production, strictly control board expansion/contraction consistency to ensure PCB dimensional accuracy, thereby guaranteeing phase consistency in the final product.

(2) The copper thickness of PCB delay lines, and the size of delay line corner burrs, do not affect phase.

Therefore, PCB processing should be controlled according to standard production parameters.

(3) This paper systematically investigates multiple critical factors potentially affecting delay line phase (including board expansion/contraction, delay line copper thickness, number of delay line corners, and delay line burrs).

It clarifies the specific impact of each factor and proposes corresponding control strategies.

The research findings provide essential reference guidelines for PCB delay line design and production, significantly enhancing phase consistency and thereby improving the overall performance of electronic devices.