Printed Circuit Board (PCB) design is a complex yet crucial process that directly influences the performance, reliability, and manufacturability of electronic products.

Among its many stages, layout and routing stand out as the most critical, requiring careful planning, precision, and adherence to design principles.

From component placement and signal flow optimization to power integrity and noise control, every decision made during the design process can significantly impact the final outcome.

Drawing from practical experience, this article outlines essential tips and best practices to help engineers avoid common pitfalls and achieve efficient, high-quality PCB designs.

Layout

Layout is a critical aspect of design.

The quality of the layout directly impacts the effectiveness of the routing; therefore, it can be said that a well-planned layout is the first step toward a successful PCB design.

In particular, the pre-layout phase involves considering the overall structure of the board, including signal flow, thermal management, and mechanical design.

If the pre-layout is flawed, all subsequent efforts will be in vain.

Considering the Big Picture

The success of a product depends on two factors: first, its intrinsic quality; and second, its overall aesthetic appeal.

Only when both aspects are well-executed can the product be considered a success.

On a PCB, component placement must be balanced, with components distributed in an orderly manner—neither too dense at one end nor too sparse at the other.

Will the PCB warp?

Have process margins been reserved?

Have marking points been reserved?

Is panelization required?

How many layers are needed to ensure impedance control, signal shielding, signal integrity, cost-effectiveness, and manufacturability?

Eliminating Basic Errors

Do the PCB dimensions match those on the manufacturing drawings? Do they meet PCB manufacturing process requirements? Are there positioning marks?

Are there any component conflicts in 2D or 3D space?

Is the component layout well-spaced and orderly? Are all components placed?

Can components that need frequent replacement be easily swapped out? Is the board easy to insert into the insertion machine?

Is there adequate spacing between thermosensitive components and heat-generating components?

Are adjustable components easy to fine-tune?

Have heat sinks been installed where heat dissipation is required? Is airflow unobstructed?

Is the signal flow smooth, and are interconnections kept to a minimum?

Do connectors (such as plugs and sockets) conflict with the mechanical design?

Have issues related to signal interference been addressed?

Bypass or Decoupling Capacitors

When routing circuits, both analog and digital devices require these types of capacitors.

A bypass capacitor, typically rated at 0.1 μF, should be connected near the power supply pins of each device.

Keep the leads as short as possible to minimize the inductance of the traces, and position the capacitor as close to the device as possible.

Basic Role of Bypass and Decoupling Capacitors

The addition of bypass or decoupling capacitors on a circuit board, as well as their placement, is considered basic knowledge in both digital and analog design, but their functions differ.

Function in Analog Circuits

In analog layout design, bypass capacitors are typically used to bypass high-frequency signals on the power supply.

Without them, these high-frequency signals could enter sensitive analog chips through the power supply pins.

Generally, the frequencies of these high-frequency signals exceed the ability of analog devices to suppress them.

If bypass capacitors are not used in analog circuits, noise may be introduced into the signal path, and in more severe cases, oscillations may even occur.

Function in Digital Circuits

For digital devices such as controllers and processors, decoupling capacitors are also necessary, but for different reasons.

One function of these capacitors is to serve as “miniature” charge reservoirs.

This is because in digital circuits, switching gate states (i.e., switching operations) typically require a large current.

When switching occurs, switching transient currents are generated on the chip and flow through the circuit board; having this additional “reserve” charge is advantageous.

If there is insufficient charge during a switching operation, it can cause significant fluctuations in the supply voltage.

Excessive voltage fluctuations can cause digital signal levels to enter an indeterminate state and are likely to trigger erroneous operation of state machines within digital devices.

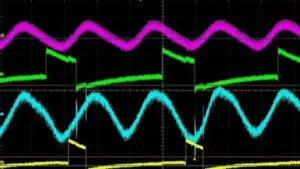

Impact of PCB Trace Inductance

The switching current flowing through the PCB traces causes voltage changes.

Since PCB traces have parasitic inductance, the voltage change can be calculated using the following formula:

V = LδI/dt

where V = voltage change, L = trace inductance, δI = change in current through the trace, and dt = time interval of the current change.

Therefore, for a variety of reasons, it is a very good practice to apply bypass (or decoupling) capacitors at the power supply input or at the power pins of active devices.

High-Current Input Power Supply

For input power supplies with high current, it is recommended to minimize trace length and area and avoid routing traces across the entire board.

Switching noise from the input has coupled to the output ground plane.

Switching noise from the MOSFETs in the output power supply affects the input power supply of the preceding stage.

If there are numerous high-current DC-DC converters on the board, they generate interference from high-voltage transients at various frequencies.

Therefore, we need to minimize the area of the input power supply to just the size necessary to carry the current.

When laying out the power supply, care must be taken to avoid routing the input power supply across the entire board.

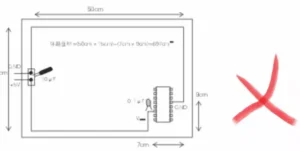

Power Lines and Ground Lines

Proper alignment of power lines and ground lines can reduce the likelihood of electromagnetic interference (EMI).

If power lines and ground lines are improperly aligned, system loops may be created, which are likely to generate noise.

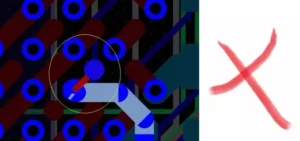

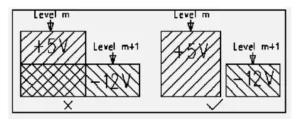

An example of a PCB design with improper alignment of power lines and ground lines is shown in the figure.

In this circuit board, separate traces are used for power and ground lines.

Due to this improper routing, the electronic components and circuits on the board are more susceptible to electromagnetic interference (EMI).

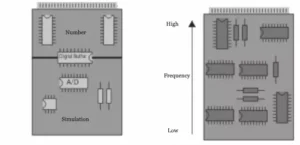

Separation of Digital and Analog Circuits

In every PCB design, the noisy portions of the circuit must be separated from the “quiet” portions (non-noisy portions).

Generally speaking, digital circuits can tolerate noise interference and are not sensitive to noise (because digital circuits have a higher voltage noise margin); conversely, analog circuits have a much lower voltage noise margin.

Of the two, analog circuits are most sensitive to switching noise. In the routing of mixed-signal systems, these two types of circuits must be separated.

The fundamentals of PCB layout apply to both analog and digital circuits.

A basic rule of thumb is to use a continuous ground plane; this principle helps mitigate the dI/dt (current-over-time) effect in digital circuits, as this effect can induce ground potentials and introduce noise into analog circuits.

The routing techniques for digital and analog circuits are essentially the same, with one exception.

For analog circuits, there is an additional consideration: digital signal lines and ground loops should be kept as far away from the analog circuit as possible.

This can be achieved by connecting the analog ground plane separately to the system ground connection, or by placing the analog circuit at the farthest end of the board—that is, at the end of the signal path.

This is done to minimize external interference on the signal path.

This is not necessary for digital circuits, as they can tolerate a significant amount of noise on the ground plane without experiencing issues.

Heat Dissipation Considerations

During the layout process, it is essential to consider heat dissipation paths and areas where heat cannot escape;

Do not place heat-sensitive components in the direct path of airflow from heat sources.

Give priority to the placement of components that are difficult to cool, such as DDR modules.

Avoid repeated adjustments caused by failing thermal simulations.

PCB Routing

In PCB design, routing is a critical step in completing the product design; it can be said that all prior preparatory work is done in anticipation of this stage.

Among all aspects of PCB design, the routing process is the most demanding, requiring the greatest precision and involving the heaviest workload.

PCB routing includes single-sided, double-sided, and multi-layer routing.

There are two routing methods: automatic routing and interactive routing.

Before automatic routing, interactive routing can be used to pre-route traces with stricter requirements. Input and output traces should avoid running adjacent and parallel to prevent reflection interference.

Ground planes should be added for isolation when necessary, and traces on adjacent layers must be perpendicular to each other, as parallel traces can easily cause parasitic coupling.

The success rate of automatic routing depends on a well-planned layout.

Routing rules can be predefined, including the number of bends in the trace, the number of vias, and the number of steps.

Generally, exploratory routing is performed first to quickly connect short traces, followed by maze-style routing.

This involves global path optimization for the connections to be routed, which can break existing routes as needed.

It also attempts to reroute the traces to improve the overall result.

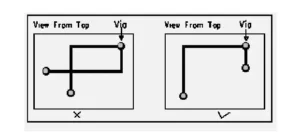

In current high-density PCB designs, through-holes are increasingly seen as inadequate, as they waste many valuable routing channels.

To resolve this issue, blind and buried via technologies have emerged.

These not only fulfill the function of through-holes but also free up numerous routing channels, making the routing process more convenient, smoother, and more efficient.

The PCB design process is both complex and straightforward. To truly master it, electronic engineering designers must gain firsthand experience to grasp its true essence.

Handling of Power and Ground Lines

Even if the routing of the entire PCB is executed flawlessly, interference caused by inadequate consideration of power and ground lines can degrade product performance and, in some cases, even affect the product’s success rate.

Therefore, the routing of power and ground lines must be treated with the utmost care to minimize noise interference generated by these lines and ensure product quality.

Every engineer involved in electronic product design understands the causes of noise between ground and power lines.

Here, we will focus solely on methods to reduce or suppress this noise:

(1) It is well known that decoupling capacitors should be added between power and ground lines.

(2) Maximize the width of power and ground traces; ideally, the ground trace should be wider than the power trace.

The recommended width hierarchy is: ground trace > power trace > signal trace.

Typically, signal traces are 0.2–0.3 mm wide, with the narrowest widths reaching 0.05–0.07 mm. while power lines range from 1.2 to 2.5 mm.

For digital circuit PCBs, wide ground traces can be used to form a loop, effectively creating a ground plane (this approach should not be used for analog circuit grounds).

(3) Use a large copper area as the ground plane; on the printed circuit board, connect all unused areas to ground to serve as ground traces.

Alternatively, use a multilayer board, with the power and ground traces each occupying a separate layer.

Ground Management in Digital and Analog Circuits

Today, many PCBs are no longer single-function circuits (digital or analog) but are instead composed of a mix of digital and analog circuits.

Therefore, when routing, it is necessary to consider the issue of mutual interference between them, particularly noise interference on ground lines.

Digital circuits operate at high frequencies, while analog circuits are highly sensitive.

For signal lines, high-frequency signals should be routed as far away as possible from sensitive analog components.

Regarding ground lines, the entire PCB has only one connection point to the outside world; therefore, the issue of shared ground between digital and analog circuits must be addressed internally on the PCB.

Within the board, digital ground and analog ground are actually separated and do not interconnect; they are connected only at the interface points where the PCB connects to the outside world (such as connectors).

There is a single short-circuit connection between the digital ground and the analog ground; please note that there is only one connection point.

Some PCBs do not share a common ground, which is determined by the system design.

Routing Signal Lines on Power (Ground) Layers

When routing on multi-layer printed circuit boards, there is often little unused space left on the signal layers.

Adding more layers would result in waste, increase production workload, and raise costs accordingly.

To resolve this issue, consider routing on power (ground) layers.

The power layer should be considered first, followed by the ground layer, as it is best to maintain the integrity of the ground layer.

Handling of Component Leads in Large-Area Conductors

In large-area grounding (electrical) systems, component leads are commonly connected to the conductor.

The handling of these leads requires comprehensive consideration.

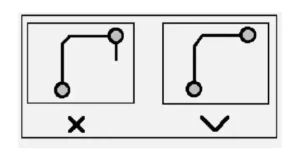

From an electrical performance perspective, it is preferable for the component lead pads to be fully connected to the copper surface; however, this approach poses certain risks to the soldering and assembly process, such as:

① Soldering requires a high-power heater.

② It is prone to causing cold solder joints.

Therefore, to balance electrical performance and process requirements, a cross-shaped pad is used, known as a heat shield (or commonly referred to as a thermal pad).

This significantly reduces the likelihood of cold solder joints caused by heat dissipation due to excessive cross-sectional area during soldering.

The treatment of component leads on the power (ground) layer of multilayer boards is the same.

The Role of the Grid System in Routing

In many CAD systems, routing is determined by the grid system.

If the grid is too dense, although the number of routing paths increases, the step size becomes too small, and the data volume in the drawing becomes excessive.

This inevitably places higher demands on device storage capacity and also significantly impacts the processing speed of the host computer and other electronic devices.

Furthermore, some paths are ineffective, such as those occupied by component pad pads, mounting holes, or alignment holes.

Conversely, a grid that is too sparse, with too few paths, significantly reduces routing efficiency.

Therefore, a grid system with a reasonable density is essential to support the routing process.

The standard distance between the legs of a component is 0.1 inches (2.54 mm), so the grid system is generally based on 0.1 inches (2.54 mm) or an integer multiple of 0.1 inches, such as 0.05 inches, 0.025 inches, or 0.02 inches.

Design Rule Check (DRC)

Once the routing design is complete, it must be thoroughly checked to ensure it complies with the rules established by the designer.

It is also necessary to verify that these rules meet the requirements of the printed circuit board manufacturing process. Generally, the following aspects are checked:

(1) Are the distances between traces, between traces and component pads, between traces and vias, between component pads and vias, and between vias reasonable and in compliance with manufacturing requirements?

(2) Are the widths of power and ground traces appropriate? Is there tight coupling (low impedance) between power and ground traces?

Are there areas on the PCB where ground traces can be widened?

(3) Have optimal measures been taken for critical signal lines, such as minimizing length, adding shielding, and clearly separating input and output lines?

(4) Do the analog and digital circuit sections have their own independent ground planes?

(5) Will graphics added to the PCB (such as icons and labels) cause signal short circuits?

(6) Modify any suboptimal trace routing.

(7) Are process lines included on the PCB? Does the solder mask meet production requirements?

Are the solder mask dimensions appropriate? Are character markings positioned over component pads to avoid affecting assembly quality?

(8) Are the outer edges of the power and ground planes on multilayer boards recessed?

If the copper foil of the power or ground planes extends beyond the board edges, it can easily cause short circuits.

Check for sharp corners, impedance discontinuities, etc.

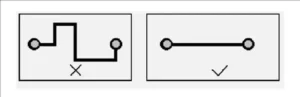

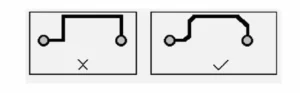

(1) For high-frequency currents, when a conductor bends at a right angle or even a sharper angle, the magnetic flux density and electric field strength are relatively high near the bend.

This results in stronger electromagnetic radiation, and the inductance at this point is relatively large, leading to higher reactance compared to obtuse or rounded corners.

(2) In digital circuit bus routing, using obtuse or rounded corners results in a smaller footprint.

Under the same trace spacing conditions, the total width occupied by the traces is 30% less than that of a right-angle bend.

Verification of the 3W and 3H Principles

(1) The routing of clock, reset, signals exceeding 100 MHz, and certain critical bus signals must comply with the 3W principle: there should be no long parallel runs on the same layer or adjacent layers, and the number of vias in the signal path should be minimized.

(2) Regarding the number of vias for high-speed signals: Some device datasheets impose strict requirements on the number of vias for high-speed signals.

According to interconnect principles, aside from essential pin fanout vias, creating unnecessary vias on inner layers is strictly prohibited.

However, when routing 8G PCIe 3.0 traces, they have used as few as four vias without issues.

(3) The center-to-center spacing between clock and high-speed signals on the same layer must strictly meet the 3H requirement (where H is the distance between the trace layer and the return plane); signals on adjacent layers must not overlap, and it is recommended to also adhere to the 3H principle.

Regarding the crosstalk issues mentioned above, there are tools available to check for them.

Routing Constraints

Routing Constraints: Layer Distribution

For RF PCBs, each layer must have a large ground plane; there should be no power planes.

The layers immediately above and below the RF routing layer must both be ground planes.

Even on mixed-signal boards, where the digital section may include power planes, the RF area must still meet the requirement of having a large ground plane on every layer.

Routing Constraints: Basic Requirements

(1) General Routing Guidelines

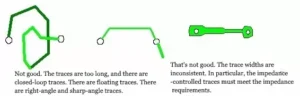

Routing should be as short as possible, avoid closed loops and sharp or right angles, maintain consistent trace widths, and ensure no floating traces.

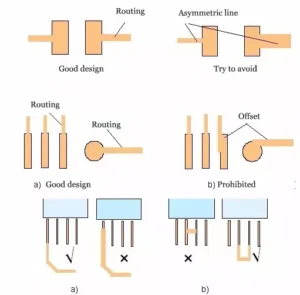

(2) Pad Routing Considerations

The routing of pads must be reasonable.

(3) Differential Signal Routing Requirements

Signal lines used for high-speed transmission must maintain impedance symmetry.

Differential lines must not cross each other; the difference in line length must not exceed 100 mils; and impedance requirements must be met between differential lines and between individual differential lines and ground.

Differential lines must not pass through more than four vias. The spacing between differential line pairs must comply with the 3W rule.

(4) Isolation Rules for High-Speed and Sensitive Signals

Clock lines, control lines, and electromagnetically sensitive lines must not be routed beneath crystal oscillators, PLL filters, analog signal processing chips, inductors, or transformers.

(5) Separation of Analog, Digital, and Power Signals

Analog signals and digital signals, power lines and control signal lines, and low-level signals must not be routed side-by-side; they should be routed on separate layers (preferably with ground isolation) or at a sufficient distance apart.

If traces on adjacent layers must cross, they must not run parallel. To minimize crosstalk, ensure sufficient spacing between traces.

When the center-to-center spacing is at least three times the trace width, 70% of the electric fields will not interfere with each other; this is known as the 3W rule.

To achieve 98% non-interference, use a 10W spacing.

Note: When routing clock lines, ensure effective isolation from data lines and control signal lines; the greater the distance, the better, and avoid routing them on the same layer whenever possible.

(6) High-Radiation Signal Placement Restrictions

High-radiation signal lines (high-frequency, high-speed, especially clock lines) should not be routed near interfaces or pull tabs to prevent external radiation.

(7) Sensitive Signal Protection and Routing Strategy

Sensitive signals (primarily referring to: weak signals, reset signals, comparator input signals, ADC reference power supplies, PLL filter signals, and the filtering sections of internal PLL circuits) should be routed as short as possible, kept away from strong radiating signals, and not placed near the board edges; they should be kept at least 15 mm away from the outer metal frame.

For long-distance routing, ground planes may be used (note that ground planes may cause impedance changes), or routing should be done on inner layers.

Additionally, for chips with low ESD tolerance, it is recommended to route traces on inner layers to reduce the likelihood of chip damage.

Routing Constraints: Power Supply

(1) Ensure proper decoupling and filtering of the power supply to prevent interference between different modules via power lines.

When routing power lines, they should be isolated from one another. Power lines should be isolated from other high-interference lines (such as CLK) using ground planes.

(2) The power supply routing for small-signal amplifiers requires isolation via ground planes and ground vias to prevent other EMI interference from entering and degrading the signal quality of the current stage.

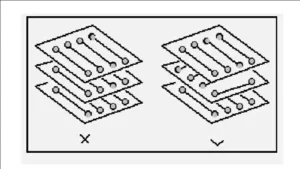

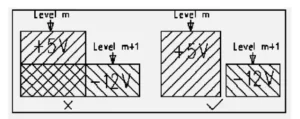

(3) Power planes should not overlap spatially.

This is primarily to reduce interference between different power supplies, especially between those with significantly different voltages.

Overlapping power planes must be avoided whenever possible; if unavoidable, consider inserting an intermediate ground plane.

Wiring Constraints: Power Supply Current-Carrying Capacity

(1) The number of vias used to route power supply traces between layers must meet the current-carrying requirements (1 A per 0.3 mm diameter via).

(2) The copper trace width in the power supply section of the PCB must be sufficient to handle the maximum current flowing through it, with a margin factored in (generally 1 A per mm of trace width).

Wiring Constraints: Grounding Methods

(1) Grounding wires should be short and straight to minimize distributed inductance and reduce interference caused by common-mode impedance.

Adjust the orientation of the filter capacitors within each group to minimize the ground loop.

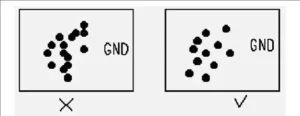

As shown in Figure 15, the three filter capacitors should be grounded toward the relevant RF components, especially the high-frequency filter capacitors.

(2) When grounding components and power supply filter capacitors on the RF main signal path require grounding, they must be grounded as close as possible to minimize component ground inductance.

(3) For components with grounded metal casings on their undersides, ground vias must be added within the component’s footprint area; signal traces and vias must not be routed on the surface layer within this footprint area;

(4) When ground traces must travel a certain distance, the trace width should be increased and the trace length minimized; traces must not approach or exceed one-quarter of the guided-wave wavelength to prevent signal radiation caused by antenna effects;

(5) Except for special purposes, isolated copper patches are not permitted; ground vias must be added to copper patches.

(6) Certain sensitive circuits and circuits with strong radiation sources should be placed in shielded chambers, which are pressed against the PCB surface during assembly.

During PCB design, a “via shielding wall” must be incorporated, which involves adding grounded vias at points where the PCB is in close contact with the shielded cavity wall.

As shown in Figure 12 below, there must be at least two rows of vias, with the rows staggered relative to each other, and the spacing between vias in the same row should be approximately 100 mils.

Routing Constraints: General Rules

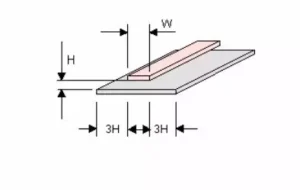

(1) RF Signal Layer Stack-up and Microstrip Structure Rules

RF signals are routed on the top layer of the PCB.

The plane layer beneath the RF signals must be a continuous ground plane to form a microstrip line structure, as shown in Figure 13.

To ensure the structural integrity of the microstrip line, the following must be observed:

Microstrip lines on the same layer must be surrounded by a ground copper pad; it is recommended that the edge of the ground copper pad be at least 3H away from the edge of the microstrip line.

Here, H represents the dielectric layer thickness. No other signal vias are permitted within the 3H range.

RF signal traces must not cross the gap in the ground plane on the second layer.

A ground copper pad must be added between non-coupled microstrip lines, and ground vias must be placed on the ground copper pad.

The distance between the microstrip line and the shielding wall should be maintained at 3H or greater.

Microstrip lines must not cross the dividing line of the ground plane on the second layer.

(2) RF Ground Clearance Requirement (3H Rule)

The spacing between the ground plane and signal traces must be ≥3H.

(3) Ground Plane Edge Via Stitching Standard

Ground vias must be added along the edges of the ground plane, spaced approximately 100 mils apart and arranged in a uniform, orderly pattern;

(4) Ground Plane Edge Quality Requirements

The edges of the ground plane must be smooth and flat; sharp burrs are prohibited;

(5) RF Trace Termination and Layout Integrity Rules

Except for special purposes, excess wire ends must not protrude from RF signal traces.

(6) RF Signal Isolation Using Ground Shielding (Co-Routing Protection)

If other RF signal traces are present near an RF signal trace, a ground plane must be placed between them, and a ground via must be added to the ground plane at intervals of approximately 100 mils to provide isolation.

(7) Isolation of RF Traces from Non-RF Interference Sources

If other unrelated non-RF signals (such as crossing power lines) are present near RF signal traces, a ground plane must be inserted between them, with a ground via placed approximately every 100 mils.

(8) RF Via EMI Control and Cross-Layer Isolation Strategy

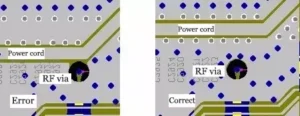

When RF signal vias are close to other internal traces—such as the power line shown in the left figure, which is near an RF signal via—EMI interference from the power line can couple into the RF traces.

Therefore, the correct routing method shown in the right figure of Figure 14 should be adopted: insert a ground plane between the power line and the RF signal via and add a ground via to provide isolation.

Similarly, when RF signal traces on inner layers are close to vias carrying other signals with strong interference (such as passing power lines), the same method of adding a ground plane and ground vias should be used.

(9) RF Routing Clearance Around Mechanical Mounting Holes

When component mounting holes are non-plated-through holes, RF signal traces should be routed away from them.

A ground plane should be inserted between the RF signal traces and the mounting holes, and ground vias should be added.

1. Routing Priorities

Prioritize critical signal lines: Power, analog small-signal, high-speed, clock, and synchronization signals should be routed first.

Prioritize density: Begin routing with the components that have the most complex interconnections on the board.

Start routing in the areas of the board with the highest density of connections.

2. Automatic Routing

Provided that the routing quality meets design requirements, an automatic router may be used to improve work efficiency.

The following preparatory work should be completed before automatic routing:

Automatic Routing Control File (DO File): To better control routing quality, routing rules should generally be defined in detail before running the software.

While these rules can be defined within the software’s graphical interface, the software offers a more effective control method: creating an automatic routing control file (DO file) tailored to the design, under which the software operates.

3. Whenever possible, provide dedicated routing layers for critical signals such as clock signals, high-frequency signals, and sensitive signals, and ensure the loop area is minimized.

If necessary, employ methods such as manual routing, shielding, and increasing safety margins to ensure signal quality.

4. The EMC environment between power planes and ground planes is poor; avoid routing signals sensitive to interference in these areas.

5. Networks with impedance control requirements should be routed on impedance control layers.

6. Rules to Follow During PCB Design

1) Ground Loop Rules:

The minimum loop rule dictates that the loop area formed by a signal line and its return path should be as small as possible.

The smaller the loop area, the lower the external radiation and the reduced susceptibility to external interference.

When partitioning the ground plane, consider the distribution of the ground plane and critical signal traces to prevent issues caused by ground plane notches;

In dual-layer board designs, while reserving sufficient space for power supplies, the remaining areas should be filled with reference ground and equipped with necessary vias to effectively connect the ground signals on both sides.

Ground isolation should be used for critical signals whenever possible.

For high-frequency designs, special attention must be paid to ground plane signal loop issues; the use of multilayer boards is recommended.

2) Crosstalk Control:

Crosstalk refers to mutual interference between different networks on a PCB caused by long parallel traces, primarily due to the effects of distributed capacitance and inductance between parallel lines.

The main measures to mitigate crosstalk are:

Increase the spacing between parallel traces and follow the 3W rule.

Insert grounded isolation lines between parallel traces.

Reduce the distance between the routing layer and the ground plane.

3) Shielding Protection

In accordance with ground loop rules, this is essentially intended to minimize the signal loop area.

It is commonly applied to critical signals such as clock signals and synchronization signals.

For particularly critical signals with very high frequencies, a shielded copper-axial cable design should be considered, where the routed lines are isolated from ground on all sides (top, bottom, left, and right).

Additionally, careful consideration must be given to effectively connecting the shield ground to the actual ground plane.

4) Rules for Controlling Trace Orientation:

Traces on adjacent layers should be oriented orthogonally to one another.

Avoid routing different signal lines in the same direction on adjacent layers to reduce unnecessary crosstalk between layers.

When this situation is unavoidable due to board structural constraints (such as certain backplanes), particularly at higher signal speeds, consider isolating each routing layer with a ground plane and isolating each signal line with a signal line.

5) Open-loop Inspection Rules for Routing:

Generally, dangling lines (wires with one end left floating) are not permitted, primarily to avoid the “antenna effect” and reduce unnecessary interference radiation and reception; otherwise, this could lead to unpredictable results.

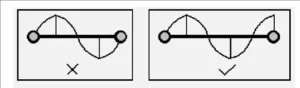

6) Impedance Matching Rules:

The trace width within the same network should remain consistent.

Variations in trace width can cause non-uniform characteristic impedance, which may result in reflections at high transmission speeds; this situation should be avoided as much as possible during design.

Under certain conditions, such as with connector leads or structures similar to BGA package leads, variations in trace width may be unavoidable; in such cases, the effective length of the inconsistent sections should be minimized.

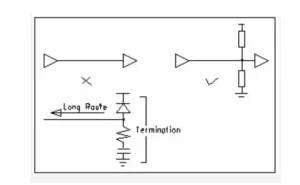

7) Rules for Terminating Transmission Lines:

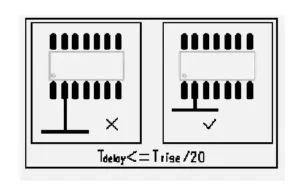

In high-speed digital circuits, when the propagation delay of a PCB trace exceeds one-quarter of the signal’s rise time (or fall time), the trace can be treated as a transmission line.

To ensure proper impedance matching between the signal’s input and output and the transmission line’s impedance, various matching methods can be employed.

The choice of matching method depends on the network’s connection configuration and the trace topology.

① For point-to-point (one output corresponding to one input) connections, either series termination at the source or parallel termination at the sink can be selected.

The former has a simple structure and low cost but results in higher delay.

The latter provides better matching performance but involves a complex structure and higher cost.

②. For point-to-multipoint (one output corresponding to multiple outputs) connections, when the network topology is a daisy chain, parallel termination at the sink should be selected.

When the network has a star topology, the approach for point-to-point connections can be used as a reference.

Star and daisy-chain topologies are the two basic types; other topologies can be viewed as variations of these basic structures, and flexible measures can be taken for matching.

In practice, factors such as cost, power consumption, and performance must be balanced; generally, perfect matching is not pursued, and it is sufficient to limit interference caused by mismatch—such as reflections—to an acceptable range.

8) Closed-loop Routing Rules:

Prevent signal lines from forming closed loops between different layers.

This issue commonly arises in multilayer board designs, and closed loops can cause radiated interference.

9) Rules for Controlling the Length of Signal Branches:

Keep the length of signal branches as short as possible; the general rule is that Tdelay ≤ Trise/20.

10) Rules for Avoiding Resonance in Trace Routing:

This applies primarily to high-frequency signal design, meaning that the length of the trace must not be an integer multiple of its wavelength to prevent resonance.

11) Rules for Controlling Trace Length:

This refers to the “short trace rule.” During design, trace lengths should be kept as short as possible to minimize interference caused by excessively long traces.

This is particularly important for critical signal lines, such as clock lines; in such cases, the oscillator must be placed very close to the component.

When driving multiple components, the choice of network topology should be determined based on the specific circumstances.

12) Chamfering Rules:

In PCB design, sharp corners and right angles should be avoided to prevent unnecessary radiation and ensure good manufacturability.

13) Component Decoupling Guidelines:

①. Add necessary decoupling capacitors to the printed circuit board to filter out interference signals from the power supply and stabilize the power signal.

In multilayer boards, the placement of decoupling capacitors is generally not as critical; however, in two-layer boards, the layout of decoupling capacitors and the power supply routing directly affect the stability of the entire system and can sometimes even determine the success or failure of the design.

②. In dual-layer board design, current should generally be filtered through a filter capacitor before being supplied to components.

At the same time, the impact of power supply noise generated by components on downstream components must be fully considered. Generally, a bus structure is preferable.

During design, the impact of voltage drops caused by excessive transmission distances on components must also be taken into account; if necessary, additional power supply filtering loops should be added to prevent potential differences.

③. In high-speed circuit design, the correct use of decoupling capacitors is critical to the overall stability of the board.

14) Component Placement Zoning/Layering Rules:

①. The primary purpose is to prevent mutual interference between modules operating at different frequencies while minimizing the routing length of high-frequency sections.

Typically, high-frequency sections are placed near interfaces to reduce routing length; however, such layouts must still account for potential interference with low-frequency signals.

Additionally, the separation of ground planes for high- and low-frequency sections must be considered; typically, the ground planes for the two sections are separated and connected at a single point at the interface.

②. For mixed-signal circuits, there is also a method of placing analog and digital circuits on opposite sides of the printed circuit board, routing them on separate layers, and isolating them with a ground plane in between.

15) Rules for Controlling Isolated Copper Pads:

The presence of isolated copper areas can lead to unpredictable issues; therefore, connecting these areas to other signals helps improve signal quality.

Typically, isolated copper areas are grounded or removed. In actual production, PCB manufacturers often add copper foil to unused areas of the board.

This is primarily done to facilitate the manufacturing process and also helps prevent warping of the printed circuit board.

The presence of isolated copper areas can lead to unforeseen issues; therefore, connecting these isolated copper areas to other signals can help improve signal quality.

Typically, isolated copper areas are grounded or removed.

In actual production, PCB manufacturers often add copper foil to unused areas of the board; this is primarily to facilitate the manufacturing process and also helps prevent warping of the PCB.

16) Integrity Rules for Power and Ground Planes:

In areas with dense through-holes, care must be taken to avoid holes connecting the cutout areas of the power and ground planes, as this creates divisions in the plane and compromises its integrity, thereby increasing the loop area for signal lines on the ground plane.

17) Rules for Overlapping Power and Ground Planes:

Different power planes should not overlap spatially.

This is primarily to reduce interference between different power sources, especially between those with significantly different voltages.

Overlapping power planes must be avoided whenever possible; if unavoidable, consider inserting an intermediate ground plane.

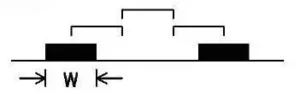

18) The 3W Rule:

To minimize crosstalk between lines, sufficient spacing between them must be ensured.

When the center-to-center spacing is at least three times the line width,

70% of the electric fields will not interfere with one another; this is known as the 3W rule.

To achieve 98% non-interference of electric fields, a spacing of 10W can be used.

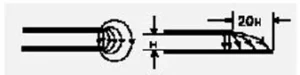

19) The 20H Rule:

Because the electric field between the power plane and the ground plane varies, electromagnetic interference radiates outward at the edges of the board. This is known as the edge effect.

The solution is to recess the power plane so that the electric field propagates only within the ground plane.

Using one H (the thickness of the dielectric between the power plane and the ground plane) as a unit, recessing the power plane by 20H can confine 70% of the electric field within the ground plane’s edge; recessing it by 100H can confine 98% of the electric field within the ground plane.

20) V. The “5-5” Rule:

This rule governs the selection of PCB layer counts: if the clock frequency reaches 5 MHz or the pulse rise time is less than 5 ns, a multilayer PCB must be used.

This is a general guideline; however, in some cases, a two-layer PCB structure may be adopted for cost or other considerations.

In such situations, it is best to designate one side of the PCB as a complete ground plane layer.

Conclusion

Successful PCB design is achieved through a balance of thoughtful planning, technical knowledge, and attention to detail across every stage of layout and routing.

By following proven guidelines—such as proper component placement, effective power and ground management, noise reduction techniques, and strict adherence to design rules—engineers can greatly enhance signal integrity and overall system performance.

Ultimately, hands-on experience combined with disciplined application of these principles is key to mastering PCB design and delivering reliable, high-performance electronic products.